## **T-Engine Design Guidelines**

# Ver. 1.00.01

TEF010-S007-01.00.01/en

June 2009

T-Engine Forum http://www.t-engine.org/

## CONTENTS

| ■ Chapter 1 Overview of T-Engine specifications                                          |    |

|------------------------------------------------------------------------------------------|----|

| 1.1. Significance of the T-Engine project and standardization of hardware specifications |    |

| 1.2. T-Engine system structure                                                           | 14 |

| ■ Chapter 2 CPU-board design methods                                                     | 19 |

| 2.1. CPU                                                                                 | 19 |

| 2.2. Memory (flash, RAM)                                                                 |    |

| Chapter 3 CPU-board implementation                                                       | 21 |

| ■ Chapter 4 CPU-board interface circuitry design                                         |    |

| 4.1. Expansion bus connector design                                                      |    |

| 4.2. Serial interface                                                                    |    |

| 4.3. PC card interface                                                                   |    |

| 4.4. LCD/Touch panel interface                                                           |    |

| 4.5. eTRON SIM card interface                                                            |    |

| 4.6. USB host interface                                                                  |    |

| 4.7. Audio input/output interface                                                        |    |

| 4.8. Compact Flash card interface (µT-Engine only)                                       |    |

| 4.9. MMC/SD card interface (µT-Engine only)                                              |    |

| 4.10. Power supply interface                                                             |    |

| ■ Chapter 5 Power management design for T-Engine hardware                                |    |

| 5.1 Power modes (e.g., power save mode)                                                  | 40 |

| 5.2. Power supply controls (power on/off)                                                | 40 |

| 5.3. Linkage with an external expansion board                                            |    |

| 5.4. Handling power failures                                                             |    |

| ■ Chapter 6 Actual examples of T-Engine design                                           |    |

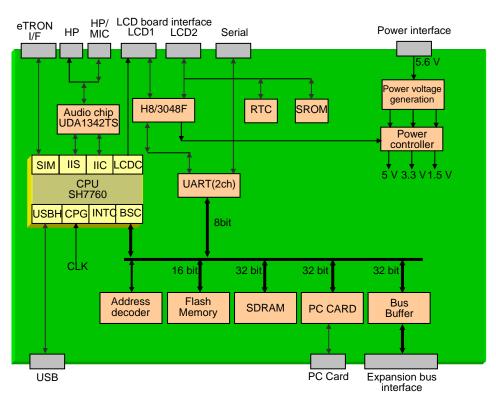

| 6.1. Example of local-bus-based T-Engine product design                                  |    |

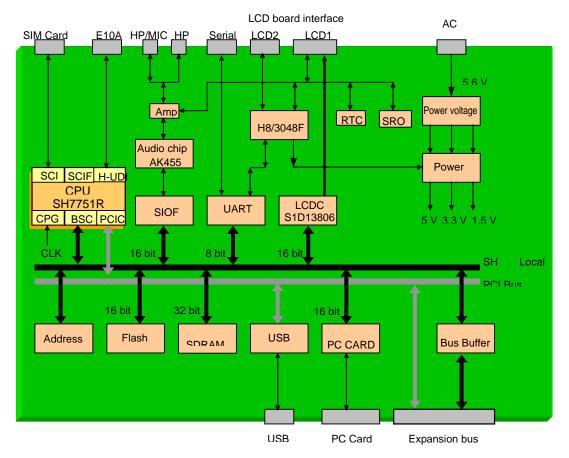

| 6.2. Example of PCI-bus-based T-Engine product design                                    | 55 |

| 6.3. Conclusion                                                                          | 64 |

#### Chapter 1 Overview of T-Engine specifications

#### 1.1. Significance of the T-Engine project and standardization of hardware specifications

#### (1) Objective and positioning of the T-Engine project

The T-Engine project is a project intended to increase the efficiency of development of software for controlling embedded systems, by increasing the ease of distributing and reusing software components such as middleware and device drivers. Centered on the T-Kernel real-time operating system, T-Engine's appeal is in the way it makes it possible to standardize the specifications of device drivers and middleware, to improve the compatibility of software, and to develop high-quality software quickly and at low cost.

Effective means of improving software compatibility and development efficiency include not just standardization of specifications for software such as operating systems but also standardization of hardware specifications and development environments as well. In the precursor to the T-Engine project, the ITRON project, only the specifications of the real-time OS were standardized, with no particular standards established for hardware or development environments. As a result, there were cases in which software could not be ported smoothly even between ITRON devices and in which software components such as middleware and device drivers did not have sufficient ease of distribution or reuse. A major strong point of the T-Engine project is the substantial improvements it has made in this area by standardizing hardware and development environments as well. Specific details of this standardization are covered later.

Since the hardware used in embedded systems varies widely, standardization of the hardware specifications for embedded systems themselves (i.e., for the final products) is not possible. This is why the T-Engine project seeks to improve software development efficiency by standardizing the hardware specifications not of the hardware of final embedded system products but of development evaluation boards used for developing prototypes and for software distribution.

A development evaluation board is a board computer used for proceeding with software development and evaluation until the hardware of the final embedded system product (e.g., in the case of a mobile phone the same hardware that will be used in the final product, in the form of a compact mobile phone) is complete. There are two types of standard specifications available for hardware for this purpose: standard T-Engine board specifications and  $\mu$ T-Engine board specifications. Each can be used for its own suitable purposes.

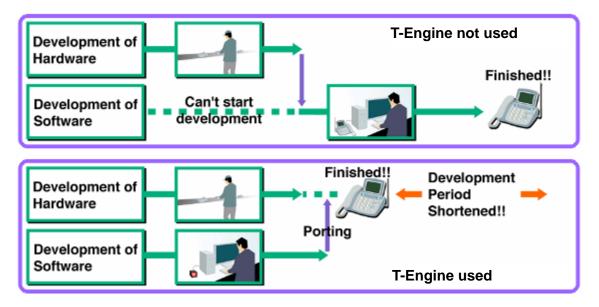

Development using a standard T-Engine board or a  $\mu$ T-Engine board — each of which is a development evaluation board — is conducted in the following steps: first, software is developed to run on the standard T-Engine board or  $\mu$ T-Engine board, and then it is ported to the final hardware when that hardware is complete. Since these two steps are involved, it might seem that this development process is complex and troublesome. However, use of a standard T-Engine board or a  $\mu$ T-Engine board has the following benefits.

First of all, use of a standard T-Engine board or a  $\mu$ T-Engine board makes it possible to proceed with development of software for a final product even before the final hardware is complete. Also, building software to some extent on a standard T-Engine board or a  $\mu$ T-Engine board makes it possible to develop prototypes of the final products early. Such prototypes can be used for demonstration purposes and for evaluation and feedback,

resulting in product improvements. Since standard T-Engine boards and  $\mu$ T-Engine boards are commercially available, if they are in stock developers can purchase and use them immediately, making it possible to proceed with software development using a structure close to that of the final product even if details of the hardware specifications for the final product have not yet been decided on or hardware development is delayed. (See Figure 1.1.1)

Figure 1.1.1: Using T-Engine to shorten the development period for an embedded system

Another benefit is the fact that standardization of the hardware specifications of the standard T-Engine and  $\mu$ T-Engine boards makes it possible to distribute software components such as OSs, middleware, and device drivers that run on such hardware as object code. As explained at the start of this chapter, the chief objective of the T-Engine project is improving the ease of distribution and reuse of software components such as middleware and device drivers. Enabling distribution of OSs and software components as object code in the same way as retail PC software or games is a major benefit toward achieving this goal.

In the past, when a developer wanted to test and evaluate software for embedded systems in an environment similar to that of a product under development, he or she needed to obtain the relevant source program and adjust and port it to make it executable on the hardware under development. However, not only does obtaining the source program in such a case often require payment of high costs, but another problem it involved was the difficulty in use for evaluation purpose due to the requirement of complex steps such as porting and compiling. In the T-Engine project, in addition to standardization of the T-Kernel real-time OS and a device driver API, standardization of the standard T-Engine and  $\mu$ T-Engine development evaluation boards resolves this problem by making it possible to distribute software components as object code.

On the other hand, the hardware specifications of the final embedded system product (e.g., the hardware specifications of a mobile phone developed using T-Engine) need not adhere to standard T-Engine or  $\mu$ T-Engine hardware specifications. These can be decided on freely in accordance with individual product plans and required specifications. For example, although the standard T-Engine board has a USB terminal, if USB is not needed for the final product it may be left out. Also, while board sizes and expansion bus connectors are standardized for the

standard T-Engine and  $\mu$ T-Engine development evaluation boards, final hardware need not be bound by these specifications. Although this point does not directly involve persons developing products using the standard T-Engine and  $\mu$ T-Engine boards, it is often misunderstood when developing T-Engine-based products, and as such should be noted.

Development evaluation boards used solely in connection with developing software for embedded systems using T-Kernel need not necessarily comply strictly with the standard T-Engine and  $\mu$ T-Engine board hardware specifications. For this reason, some T-Engine devices for development and evaluation purposes (T-Engine Appliances) have software structures including T-Kernel that comply with T-Engine specifications but hardware specifications that differ from those of standard T-Engine and  $\mu$ T-Engine.<sup>\*1</sup>

The standard T-Engine and  $\mu$ T-Engine board specifications can be used as reference specifications for development and evaluation of overall hardware aspects including the physical forms of boards, connector positions, and expansion bus connectors (covered below). The standardization of standard T-Engine and  $\mu$ T-Engine board size and connector positions is very convenient when, for example, preparing a mockup for demonstration purposes by putting a case on a prototype developed using T-Engine. Also, products such as expansion FPGA boards and universal boards that can be used with multiple standard T-Engine and  $\mu$ T-Engine devices are available on the market. These have also benefited from standardization of specifications, including those for hardware, making possible such distribution of these optional hardware components.

\*1: Examples include the Teacube/VR5701 evaluation kit and Teaboard2/ARM920-MX1. For more information on each of these, see: http://www.t-engine4u.com/

#### (2) Standard T-Engine and µT-Engine

As noted above, there are two types of specifications for T-Engine development evaluation boards: standard T-Engine and  $\mu$ T-Engine. Either of these can be chosen for use as appropriate for the size and purpose of the target embedded device.

Standard T-Engine is a standardized specification for development evaluation boards targeting development of devices with relatively high-level user interfaces such as GUIs using LCDs and touch panels. This standard also requires a CPU with a memory management unit (MMU). Use of an MMU promotes modularization of programs and increases the efficiency of software development for large-scale systems. The standard T-Engine hardware specifications reflect the high level of need for an MMU for supporting the running of dynamic applications such as those seen in PDAs.

On the other hand,  $\mu$ T-Engine is intended for devices with relatively small-scale user interfaces and used to run fixed applications for control purposes. As such, it primarily targets the type of projects that would have used ITRON in the past.

Specifications for board size and connector positions also are standardized for each of these boards. While the standard T-Engine has a CPU board size of 75 mm x 120 mm,  $\mu$ T-Engine has a CPU board size even more compact at 60 mm x 85 mm. Also, while the standard T-Engine has a PC card slot and USB,  $\mu$ T-Engine has a Compact Flash (CF) card slot as well as an MMC or SD card slot. Table 1 shows the differences between the specifications of each board.

T-Kernel, the standard real-time OS for T-Engine, runs on both standard T-Engine and  $\mu$ T-Engine, with no differences in specifications between the two boards. Also, since peripheral I/O differences are absorbed by device drivers, in principle higher layer middleware and applications will run on both standard T-Engine and  $\mu$ T-Engine. However, standard T-Engine requires an MMU while the CPU on a  $\mu$ T-Engine board will not necessarily have an MMU. This difference may lead to limitations on use of some middleware such as T-Kernel Standard Extension.

|                       | Standard T-Engine specifications           | μT-Engine specifications                        |

|-----------------------|--------------------------------------------|-------------------------------------------------|

| CPU                   | 32 bits or more                            |                                                 |

| MMU                   | Required                                   | Optional                                        |

| RAM capacity          | appropriate                                |                                                 |

| Flash memory capacity | appropriate                                |                                                 |

| Serial I/O            | 115.2kbps or faster                        |                                                 |

| Real-time clock       | Y                                          |                                                 |

| Audio I/O I/F         | Y (IN: 1ch, OUT: 2ch)                      | Ν                                               |

| eTRON Card I/F        | Y                                          |                                                 |

| LCD I/F               | Y                                          | Ν                                               |

| USB Host I/F          |                                            |                                                 |

| Expansion board I/F   | Y                                          |                                                 |

| Other I/F             | PC Card slot (Type II) x 1<br>USB host x 1 | CF card slot (Type II) x 1<br>MMC card slot x 1 |

| Board size            | 75 mm x 120 mm                             | 60 mm x 85 mm                                   |

Table 1.1.1: Comparison of standard T-Engine with  $\mu$ T-Engine

(3) Characteristics of T-Engine hardware specifications

Specifications and functions of the standard T-Engine board and the  $\mu$ T-Engine board that could be considered characteristic are described below. See the relevant specifications documents for each board concerning specific specifications.

#### • Free implementation of CPUs and peripheral devices

Although a wide range of hardware specifications, including functions of peripheral devices, have been standardized for standard T-Engine and  $\mu$ T-Engine, the only required standard for the core component — the CPU — is that it be at least a 32-bit CPU. Developers have complete freedom in choosing architecture and other specifications. Actual standard T-Engine and  $\mu$ T-Engine boards have been developed featuring a wide range of CPUs, centered on SH, MIPS, and ARM CPUs.

Although a wide variation in CPUs can have some drawbacks in regard to standardization, since CPUs for embedded devices face a wide range of requirements such as those concerning chip cost, power consumption, and on-board peripherals in addition to architecture and performance, restricting CPUs would be difficult. Also, since in the future a great number of semiconductor companies is likely to develop a wide range of new CPUs in response to these requirements, it would not be desirable for T-Engine standardization to limit the range of CPUs that could be used.

At the same time, for the most part differences in CPUs can be absorbed in the CPU-dependent portions of compilers and T-Kernel, thus minimizing their effects on middleware and applications. This is why the T-Engine project lets developers freely choose CPUs. This can be said to reflect strongly the specific circumstances of embedded systems and is contrary to practice in the world of PCs and game consoles, in which CPUs and other hardware components are heavily standardized.

In addition, although with regard to peripheral devices functions such as USB, PCM,PC Card and CF interfaces are standardized, aspects of implementation methods such as peripheral-device control chips are not standardized. Since there are also no particular standards specified with regard to the division of roles between hardware and software (device drivers), there is no need to realize all functions using hardware. Device drivers may be used to assist in implementing functions. Still, since development of device drivers is not a simple task, it can be said that unless there are specific plans for development of a device driver it would be less troublesome to use peripheral-device control chips already used commonly in standard T-Engine and  $\mu$ T-Engine devices, as much as possible. Using peripheral-device control chips already used in T-Engine devices makes it possible to reduce development costs for the entire system by simplifying the device-driver porting process.

• Standardization of board specifications such as physical size, connector positions, and screw positions

As noted above, the T-Engine standard covers not just the functions of peripheral devices for the development evaluation boards but also board specifications such as physical size, connector positions, and screw positions. Although these points are not related to software compatibility, they are very convenient for aspects of development such as designing the exteriors of demonstration models, because they make it easy to share prototype cases and installation hardware.

An optional product on the market that utilizes the benefits of this standardization of specifications such as physical size is the T-Engine Development Bench.<sup>\*2</sup> This product is a set of hardware including, among others, an acrylic stand to which the standard T-Engine board and the  $\mu$ T-Engine board can be attached, an LCD-board cover, a plastic board that makes it easy to carry the standard T-Engine board around, and special supports. It is very useful for purposes such as protecting boards and improving their portability and appearance. Since this product is not dependent on the model of T-Engine (or type of CPU), it can be used with all T-Engine boards, including

standard T-Engine boards and  $\mu$ T-Engine boards yet to be developed. This is possible because the board sizes and positions of screw holes and connectors are standardized for standard T-Engine boards and  $\mu$ T-Engine boards.

\*2: Now under development by Personal Media Corp. See: http://www.t-engine4u.com/

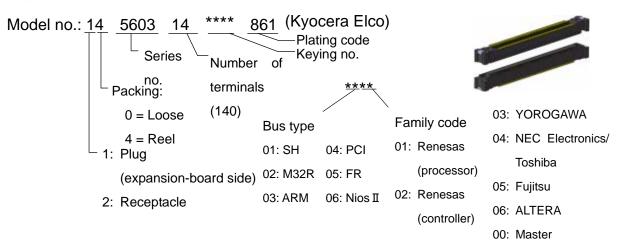

• Newly developed expansion bus connector with keying (from Kyocera Elco)

Standard T-Engine and  $\mu$ T-Engine CPU boards feature standardized T-Engine expansion bus connectors, which can be used to stack expansion boards atop CPU boards. This expansion bus connector has a pitch of 0.5 mm and 140 pins and was developed by Kyocera Elco as a new connector for the T-Engine project. <sup>\*3</sup>

\*3: See: http://www.kyocera-elco.com/prdct/type/board/5603.html This connector is available from Personal Media Corp. See: http://www.t-engine4u.com/products/connectors.html

From the stand point of practical efficiency, the standard T-Engine and µT-Engine hardware specifications do not standardize specifications such as expansion bus connector pin arrangements, protocols, or timing, focus on practical efficiency, . As a result, such specifications vary by CPU. (Arrangements are standardized for only a very small selection of pins such as power and ground pins.)

Although standardization of physical board size also requires specification of physical forms for connectors, using the same connector with separate CPUs having different bus specifications would involve the risk of hardware damage due to possible incorrect insertion of boards. The expansion bus connector developed for T-Engine use solves this problem using different types of notch patterns in the connector housing (referred to as keying). This makes it possible to differentiate logically which individual connectors can and cannot be inserted. For example, the T-Engine/SH7751R CPU board with an SH7751R on board uses an expansion bus connector with the keying 04-01. By selecting the same keying for an expansion board for use with the T-Engine/SH7751R, it is possible to produce expansion boards that cannot be inserted into T-Engine units using CPUs other than the SH7751R.

Under this method, by not using any notches it is possible to create master expansion bus connectors that can be inserted into any connector regardless of its keying. Referred to as "00-00" keying, this connector keying is useful when building expansion boards that can be used with any CPU, such as universal boards and expansion FPGA boards. However, since as noted above such connectors are also subject to incorrect insertion, they should be used with care.

Furthermore, some expansion bus connectors use keying effectively to enable multiple specific combinations. For example, expansion bus connectors using the keying 04-00 and expansion boards using those connectors can be inserted into connectors using the pattern "04-xx" (i.e., 04-01, 04-02, etc.). In fact, a number of standard T-Engine and  $\mu$ T-Engine boards with PCI-compatible buses have been assigned the keying 04-XX. By setting the keying of an expansion board for connecting to a PCI-compatible bus to 04-00, it is possible to insert the boards to a T-Engine/SH7751R board with the keying 04-01 as well as to a T-Engine/Vr5701 board with the keying 04-04. (Both of these have PCI-compatible buses.)

On the other hand, different keying (01-XX, 02-XX, etc.) is assigned to T-Engine boards with no PCI-compatible buses. For this reason, an expansion boards with the keying 04-00 cannot be inserted into such a board. In this way, incorrect insertion can be prevented based on whether or not a PCI-compatible bus is used. It is also possible to build, for example, expansion boards that can be inserted into a T-Engine/SH7751R board but cannot be inserted incorrectly into a T-Engine/VR5701 board, for example by using the bus-connector keying 04-01 for an expansion board using the T-Engine/SH7751R's local bus.

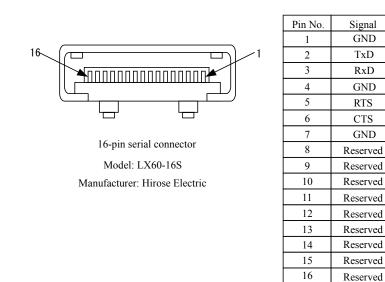

#### • Serial connectors and cables

Standard T-Engine and µT-Engine come with RS232C serial port for debug console during development. All models in standard T-Engine and µT-Engine family use 15-pin RMC-EA15MY-OM15-MC1 manufactured by HONDA TSUSHIN KOGYO CO., LTD., LX60-16S manufactured by HIROSE ELECTRIC CO., LTD., or the compatible products for serial port connector.

Serial cables for connecting this connector to the standard DSUB-9 connector used as a serial port on PCs and other devices appear to be provided often with products such as standard T-Engine boards and  $\mu$ T-Engine boards and the T-Engine Development Kit<sup>\*4</sup> combining this hardware with software such as an OS and a development environment. From the opposite perspective, when developing and providing a standard T-Engine or  $\mu$ T-Engine board it might be necessary to include this serial cable in addition to an AC adapter.

- \*4: Available from Personal Media Corp. See: http://www.t-engine4u.com/

- (4) Functions not included in standard T-Engine hardware specifications

Although T-Engine specifications cover peripheral functions needed by standard T-Engine and  $\mu$ T-Engine boards, these are only the minimum required functions. There would be no particular problems with adding other functions. In fact, standard T-Engine boards and  $\mu$ T-Engine boards with the following functions added are available on the market, with these added functions serving as the strong points of the individual products.

• VGA output connector

Makes it possible to connect the device to a PC's LCD monitor or other device to display graphics.

• Additional serial port

Makes it possible to use a second serial port for control by applications or other use, in addition to the serial port for use with a debugging console.

• USB function

Makes it possible to use the USB function feature in addition to the USB-host feature required by standard T-Engine.

• IDE connector

Features a connector that can be connected to an IDE hard drive, making it possible to connect and use a 2.5-inch hard drive.

• LAN connector

In T-Engine, LAN connection is often realized with extension board. However, there are also standard T-Engine boards equipped with LAN connector.

• CAN and other I/Os

Enables I/Os such as CAN interfaces supported by the CPU, for use by device drivers and applications.

• Other

In some cases, minor input/output functions such as DIP switches, LED, and GPIO can be used.

In some cases, the above peripheral functions may be provided via small separate boards known by names such as connector boards and I/O boards.

(5) Specific examples of T-Engine boards, and relations with standard hardware specifications

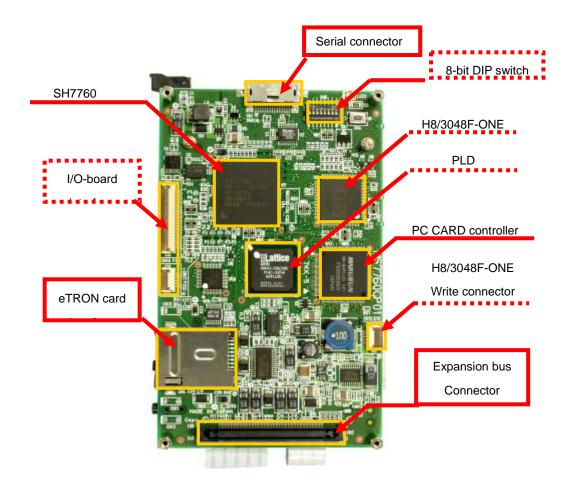

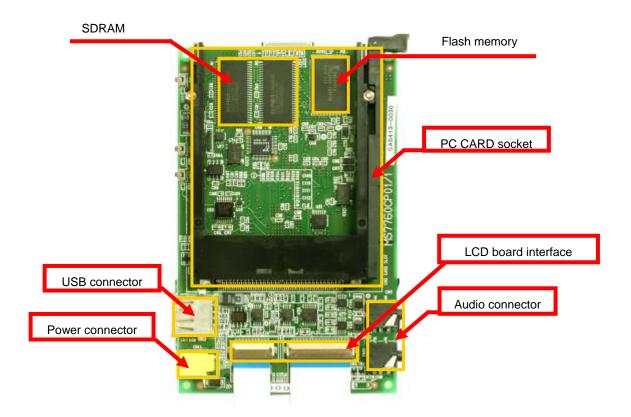

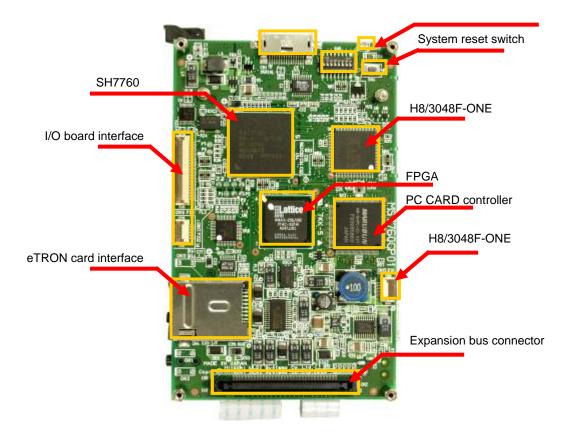

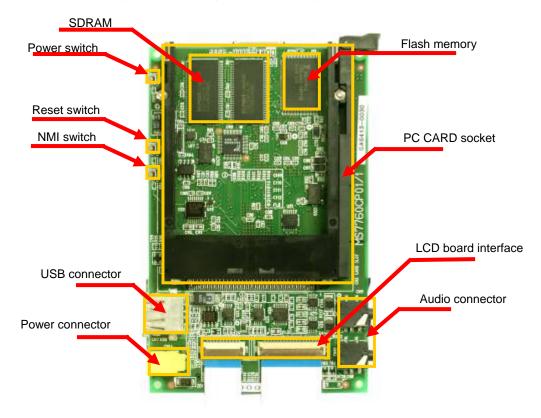

As a summary of this chapter, Figures 1.1.2 and 1.1.3 show specific arrangements of implementation of CPUs and peripheral-device control chips, connector, etc. on a standard T-Engine board actually available on the market (T-Engine/SH7760). Table 1.1.2 shows the relationship with standard T-Engine hardware specifications. Use these for reference purposes when learning about T-Engine hardware specifications.

Table 1.1.2: Photographs of a T-Engine/SH7760 board (Figures 1.1.2 and 1.1.3) and relations with standard hardware specifications

| Legend     | Meaning                                   | Specific details in T-Engine/SH7760          |

|------------|-------------------------------------------|----------------------------------------------|

| Solid      | Connector whose position and form are     | Serial connector, eTRON SIM card interface   |

| outlines   | covered in standard T-Engine hardware     | (SIM connector), expansion bus connector, PC |

|            | specifications                            | Card connector, LCD board interface, USB     |

|            |                                           | connector, audio connector, power connector  |

| Dotted     | Connectors etc. added to this T-Engine    | I/O-board interface, 8-bit DIP switch        |

| outlines   | individually and not included in standard |                                              |

|            | T-Engine hardware specifications          |                                              |

| Solid      | Chips that are functionally required in   | SH7760 (CPU), PC Card controller, SDRAM,     |

| underlines | standard T-Engine hardware                | flash memory                                 |

|            | specifications but whose position,        |                                              |

|            | installation direction, etc. are not      |                                              |

|            | specified                                 |                                              |

| Dotted     | Chips implemented for realizing the       | H8/3048F-ONE, H8/3048F-ONE write             |

| underlines | functions of a CPU board, but not         | connector, PLD                               |

|            | covered in standard T-Engine hardware     |                                              |

|            | specifications                            |                                              |

Figure 1.1.2: Photograph of T-Engine/SH7760 board, and component structure (CPU side)

Figure 3: Photograph of T-Engine/SH7760 board, and component structure (underside)

## 1.2. T-Engine system structure

1.2.1. T-Engine board structure and optional products

In addition to standard T-Engine and  $\mu$ T-Engine CPU boards featuring a wide range of CPUs, the T-Engine lineup includes a wealth of expansion boards and optional products. The expansion boards and optional products include some that may be combined with multiple CPU boards, so that even newly developed standard T-Engine and  $\mu$ T-Engine CPU boards may be able to use existing expansion boards and optional products. Be sure to refer to the range of existing products when developing boards.

## (1) CPU board

As of November 2007, the standard T-Engine and  $\mu$ T-Engine CPU boards shown in Table A1 of Appendix A either had been developed or were under development.

## (2) Expansion LAN board

Since a standard T-Engine or µT-Engine CPU board does not have an on-board LAN function, a PC LAN card or an expansion LAN board must be used. Expansion LAN boards are available corresponding to the types of keying used by expansion bus connectors. Specifically, expansion LAN boards are available for use with T-Engine/SH7727 and SH7760 (keying: 01-01), with all T-Engine/ARM models (keying: 03-03), with T-Engine/SH7751R (keying: 04-01), and with T-Engine/VR and TX (keying: 04-04).

In addition, we also have models which have LAN port on connector board attached to CPU board such as T-Engine/PPC-V4FX, and models which come with LAN expansion board such as  $\mu$ T-Engine/M32104.

## (3) LCD board

The standard T-Engine CPU board has an interface for connecting an LCD board. An LCD board with a touch panel can be connected to this interface. The LCD board can be used with all standard T-Engine models. Also, since this LCD board has a button with a "O" on it and one with an "×" on it and a directional button, it can be used for minor HMI building and testing.

In some cases (e.g., T-Engine/SH7727), an LCD board comes with the CPU board, while in other cases it must be purchased separately.

## (4) Debugging board

Basically, a debugging board is used when connecting to ICE. However, some models do not require a debugging board when connecting to ICE and some require connection to ICE using a different method, and some CPU boards come together with debugging boards. Be sure to check information on the model you will use.

## (5) Expansion FPGA board

Expansion FPGA boards for T-Engine use, featuring field programmable gate arrays (FPGAs) from major manufacturers Altera and Xilinx, have been developed that can be used by connecting them with (most) standard T-Engine and  $\mu$ T-Engine CPU boards. Using an expansion FPGA board makes it possible to develop the hardware needed by prototypes and final products even more quickly and more efficiently.

## (6) Universal expansion board

So that expansion boards can be created by hand for purposes such as development, evaluation, and testing, expansion universal boards are available as options for some standard T-Engine and  $\mu$ T-Engine models.

Although the specialized T-Engine/ $\mu$ T-Engine expansion bus connector described in the next section can be used for building expansion boards for T-Engine use, since this is a 0.5-mm pitch, 140-pin connector wiring it by hand is difficult. In such a case, use of a universal expansion board is recommended.

## (7) Specialized T-Engine/µT-Engine expansion bus connector

The expansion bus connector described above, developed as a new connector for the T-Engine project, is available on the market as an option for use with T-Engine. When obtaining one of these, use caution with regard to keying and plug/receptacle differentiation.

## (8) T-Engine Development Bench

This product is an optional set of hardware including, among others, an acrylic stand and cover for protecting the standard T-Engine CPU board and LCD board, LCD-board buttons, and supports and screws for keeping the four corners of the boards in place.

Although T-Engine boards can be used in bare state, in consideration of factors such as ease of transporting them for demonstration and testing purposes and ease of handling, it would be desirable for the boards to be protected physically to some degree. The T-Engine Development Bench can be used for this purpose. It can be used in various ways. For example, the plastic cover can be used as a simple portable case and the thick acrylic base can be used as a stand. (See Figure 1.2.1) It can handle additional expansion boards through the addition of supports and using longer screws.

Figure 1.2.1: T-Engine Development Bench

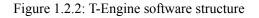

## 1.2.2. T-Engine software structure

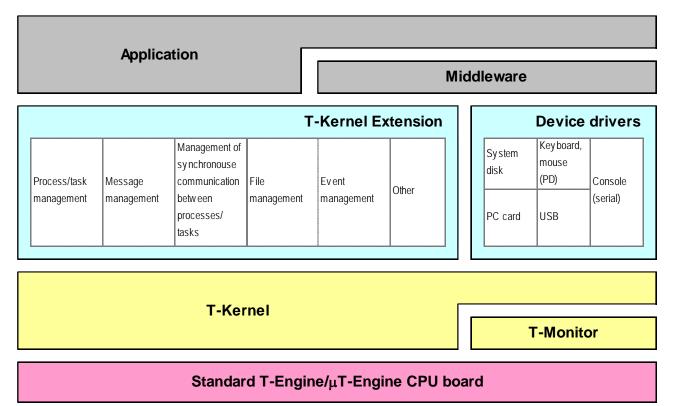

Although this document is intended primarily for hardware developers, the T-Engine software structure is described here to improve understanding of the T-Engine platform.

When starting up a T-Engine system, first of all software known as T-Monitor will start, to boot the real-time OS T-Kernel, device drivers, and other software. Refer to Figure 5 below to help understanding of the following description of the T-Engine software structure.

#### (1) T-Monitor

T-Monitor runs in standard T-Engine and  $\mu$ T-Engine Flash ROM, handling tasks such as self-diagnosis and initialization of hardware immediately following powering the system on, booting the OS, and interactive debugging (such as memory reference and break-point configuration) under a non-OS environment. It also handles processing of some interrupts and exceptions while the OS is running. In addition, it has monitoring-service functions that run in a non-OS environment, such as input of characters to and output of characters from the console and disk access, making it usable for minor debugging. The functions of T-Monitor are similar to those of a PC's BIOS.

#### (2) T-Kernel

As the standard real-time OS for standard T-Engine and  $\mu$ T-Engine, T-Kernel is a platform for executing a wide range of middleware and applications. In addition to its basic functions as a real-time kernel similar to ITRON (T-Kernel/OS), T-Kernel has the T-Kernel/SM (System Manager) function for increasing ease of middleware distribution and the T-Kernel/DS (Debugger Support) function, which is useful for implementing software task debuggers.

To ensure more complete software compatibility, the T-Engine project has standardized the implementation of the T-Kernel real-time kernel and released its source code.

## (3) T-Kernel Extension

T-Kernel Extension is middleware (basic middleware) for functional expansion of the OS, implemented using T-Kernel subsystem functions. It provides higher-level OS functions such as virtual memory using MMU, file management, and process management, and functions useful for modularization of programs.

T-Kernel Standard Extension (TKSE) is a typical example of T-Kernel Extension. The equivalent capability of UNIX kernel and its file system layer can be achieved by combining TKSE with T-Kernel. These are referred to as Ported Extensions. Examples include T-Linux, which runs Linux on T-Kernel, and T-JV, which runs Java on T-Kernel.

The combination of T-Kernel with T-Kernel Standard Extension (TKSE) makes it possible to realize functions corresponding to UNIX's kernel and file-system layers. Since implementation of TKSE requires MMU, it cannot be used on some  $\mu$ T-Engine platforms with no MMU.

#### (4) Device drivers

Device drivers make access to various peripheral devices available for general use. Since under T-Kernel the application program interface (API) used in calling device drivers from application tasks and the API used in registering new device drivers are standardized, a high level of compatibility can be ensured both for device drivers themselves and for the applications that use devices. In addition, for devices such as serial ports and system disks (CF/MMC cards) that come with or can be connected to standard T-Engine boards and µT-Engine boards, functions dependent on individual devices are also standardized.

T-Engine device drivers can also be loaded dynamically. In other words, there is no need to link all drivers when

building a system or to load all drivers in advance when starting up a system. Rather, new drivers can be loaded and executed while the system is running. Used property, this function enables functions like the "plug and play" functions of a PC and live insertion and removal of peripheral boards. This function is especially useful for devices such as PC cards and USB peripherals, with hardware compatible with live insertion and removal.

## (5) Other middleware

A wide range of middleware has been implemented at an even higher level than T-Kernel and T-Kernel Extension. For example, the PMC T-Shell<sup>\*5</sup> GUI middleware handles GUI-related processing, such as rendering of images and text to the screen and management of windows and components. Also, a number of high-level functions have been implemented as applications running on PMC T-Shell. These include implementation of the simple scripting language known as Microscript and an HTML browser. This middleware is useful for increasing the efficiency of developing embedded systems including GUIs.

\*5: See: http://www.t-engine4u.com/

## ■ Chapter 2: CPU-board design methods

2.1. CPU

Standard T-Engine specifications require a 32-bit or higher CPU with a memory management unit (MMU) on board. While  $\mu$ T-Engine specifications require a 32-bit CPU, the MMU is optional.

Existing standard T-Engine and  $\mu$ T-Engine boards feature the following CPUs:

(as of June 2009)

[Standard T-Engine]

| CPU         | Details                                  | Manufacturer              |

|-------------|------------------------------------------|---------------------------|

| SH7727      | SH3-DSP Core, 96 MHz                     |                           |

| SH7720      | SH3-DSP Core, 133 MHZ                    |                           |

| SH7751R     | SH-4 Core, 240 MHz                       | RenesasTechnology         |

| SH7760      | SH-4 Core, 200 MHz                       |                           |

| SH7780      | SH-4A Core, 400 MHz                      |                           |

| VR5500A     | MIPS Core, 400 MHz                       | NEC Electronics           |

| VR5701A     | MIPS Core, 333 MHz                       | NEC Electronics           |

| TX4956      | MIPS Core, 400 MHz                       | Toshiba                   |

| ARM720-LH7  | ARM720T Core, 77.4 MHz                   | – NXP                     |

| ARM922-LH7  | ARM922T Core, 200 MHz                    | INAP                      |

| ARM926-MB8  | ARM926EJ-S Core +ARM946E-S Core, 200 MHz | Fujitsu MicroElectoronics |

| ARM926-MX21 | i.MX21, ARM926EJ-S Core, 266 MHz         | – Freescale               |

| ARM920-MX1  | i.MX1, ARM920T Core, 200 MHz             | Ticescale                 |

| PowerPC     | PPC-V4FX Core, 300MHz                    | XILINX                    |

[µT-Engine]

| CPU          | Details                | Manufacturer    |

|--------------|------------------------|-----------------|

| SH7145       | SH2 Core, 50 MHz       |                 |

| M32104       | M32R Core, 216 MHZ     | Renesas         |

| M32192       | M32R-FPU Core, 160 MHz |                 |

| V850E/MA3    | V850E1 Core, 80 MHz    | NEC Electronics |

| VR4131       | MIPS Core, 200 MHz     | NEC Electronics |

| Nios II      | 32-bit RISC            | Altera          |

| ARM7-LH79532 | ARM7TDMI Core, 50 MHz  | NXP             |

## 2.2. Memory (Flash Memory, RAM)

With regard to memory, specifications do not include requirements for types or capacities of ROM or RAM. Memory size is determined by the needs of the CPU and applications used.

Existing standard T-Engine and  $\mu$ T-Engine boards feature the following memory configurations:

| CPU         | ROM                  | RAM                |

|-------------|----------------------|--------------------|

| SH7727      | 8 MB (Flash Memory)  | 32 MB (SDRAM)      |

| SH7720      | 8 MB (Flash Memory)  | 64 MB (SDRAM)      |

| SH7751R     | 8 MB (Flash Memory)  | 64 MB (SDRAM)      |

| SH7760      | 8 MB (Flash Memory)  | 64 MB (SDRAM)      |

| SH7780      | 16 MB (Flash Memory) | 128 MB (DDR-SDRAM) |

| VR5500A     | 16 MB (Flash Memory) | 128 MB (SDRAM)     |

| VR5701A     | 16 MB (Flash Memory) | 128 MB (DDR-SDRAM) |

| TX4956      | 16 MB (Flash Memory) | 128 MB (SDRAM)     |

| ARM720-LH7  | 8 MB (Flash Memory)  | 32 MB (SDRAM)      |

| ARM922-LH7  | 8 MB (Flash Memory)  | 32 MB (SDRAM)      |

| ARM926-MB8  | 16 MB (Flash Memory) | 64 MB (SDRAM)      |

| ARM926-MX21 | 16 MB (Flash Memory) | 64 MB (SDRAM)      |

| ARM920-MX1  | 16 MB (Flash Memory) | 64 MB (SDRAM)      |

| PPC-V4FX    | 16 MB (Flash Memory) | 128 MB (SDRAM)     |

[µT-Engine]

| CPU          | ROM                                     | RAM                              |

|--------------|-----------------------------------------|----------------------------------|

| SH7145       | 256 KB (On board) + 1 MB (Flash Memory) | 8 KB (On board) + 1 MB (SRAM)    |

| M32104       | 4 MB (Flash Memory)                     | 64 KB (On board) + 16 MB (SDRAM) |

| M32192       | 1 MB (On board)                         | 176 KB (On board) + 1 MB (SRAM)  |

| V850E/MA3    | 512 KB (On board)                       | 32 KB (On board) + 8 MB (SDRAM)  |

| VR4131       | 16 MB (Flash Memory)                    | 32 MB (SDRAM)                    |

| Nios II      | 4 MB (Flash Memory)                     | 16 MB (SDRAM)                    |

| ARM7-LH79532 | 4 MB (Flash Memory)                     | 16 MB (SDRAM)                    |

## ■ Chapter 3 CPU-board implementation

CPU-board specifications include requirements for board size (120 mm x 75 mm), board thickness (1.6 mm), connector-position tolerance (+/- 2 mm), and hole-position tolerance (+/- 0.3 mm). They also cover the implementation and hole positions for the following types of connectors and switches.

Readers are referred to the T-Engine Hardware Specifications (TEF010-S001-01.01.02/en) for the details of implementation specifications.

[Standard T-Engine:]

- 1) eTRON SIM card connector

- 2) PC Card slot

- 3) USB HOST connector

- 4) Serial connector

- 5) Power switch

- 6) Reset switch

- 7) NMI switch

- 8) Expansion bus connector

- 9) Power connector

- 10) Headset connector

- 11) Headphone output connector

- 12) Hole positions at four Corners

- 13) LCD connector

## [µT-Engine]

- 1) eTRON SIM card connector

- 2) Compact Flash card connector

- 3) MMC connector

- 4) Serial connector

- 5) Power switch

- 6) Reset switch

- 7) Expansion bus connector

- 8) Hole positions at four Corners

Since positions are specified for a large number of components, sufficient consideration is required concerning reducing the number of components and component layout. Although the height of components is not covered in specifications, since a T-Engine expansion board connects to the CPU board by stacking, care is also required concerning the height of components used on the CPU board.

#### ■ Chapter 4 CPU-board interface circuitry design

#### 4.1. Expansion bus connector design

4.1.1. Basic concept

Standard T-Engine and  $\mu$ T-Engine (hereinafter, except as specified otherwise these are both referred to as "T-Engine") have the minimum required interfaces for developing programs, in a compact size easy to embed in prototype devices. For this reason, in general the required input/output interfaces, peripheral LSIs, etc. are included on expansion boards that connect to the T-Engine board. The T-Engine board has connectors (expansion bus connectors) for expansion boards and for exchanging signals and power supplies. Primarily, specifications are defined for the following matters related to these connectors:

- Connector type (size, number of pins, etc.)

- Connector installation position

- Power supply pin position (four-pin only) and voltage

- Ground pin position (four-pin only)

In this way, although aspects other than those listed above (in particular, signal specifications) are not standardized, in consideration of convenience to the T-Engine user efforts have been made to ensure the sharing of such aspects as much as possible. As a result, these can be categorized into a number of groups of shared signal specifications. When developing a new T-Engine, it could be considered desirable to ascertain the latest circumstances with regard to these matters and to conform to existing specifications as much as possible.

## 4.1.2 Types of expansion buses (signal specifications)

## [Ground and power supply]

The four pins nos. 137 - 140 are assigned as ground pins, and the four pins nos. 133 - 136 are assigned as power supply pins for power supplied from the expansion board to the T-Engine board. Power supply voltage is specified at 5V + -5%. For this reason, the T-Engine board is designed to run over a broader range than 5V + -5%.

The T-Engine board also has a power connector for use when using the board alone. Under the basic specifications, when connecting an expansion board, power is not supplied to the main board's power connector. Rather, power is supplied only from the expansion board side. However, it is anticipated that under actual conditions of use power might be supplied from the main board side mistakenly, damaging both the expansion board and the main board. It would be desirable to use countermeasures such as inserting a diode on the T-Engine board side.

The four power supply pins are referred to as VBAT. This name is a relic of the fact that its design initially assumed power would be supplied from a secondary battery.

## [Groups]

Figure 4.1.1 shows an overview of the T-Engine expansion bus connector. See Appendix B (T-Engine Expansion bus connector Signal List) concerning assignment of expansion bus connector signals. Complying with existing types as much as possible not only makes it possible to use various existing expansion boards but also can lead to reduced development costs by eliminating the need to ask the manufacturer to supply a connector with a new key. In particular, T-Engine boards with PCI buses currently have been standardized on the 04-XX type.

In addition, even when it is difficult to match signal specifications with any existing type, an FPGA board can be connected without using a converter board simply by matching the ground pin to an existing board.

Note that Figure 4.1.1 and Appendix B are subject to change without notice and that the accuracy of their content is not guaranteed.

| SERIE           | SERIES 5603 KEY-VARIATION      |            |          | 2N    |          |                                        |       |            |

|-----------------|--------------------------------|------------|----------|-------|----------|----------------------------------------|-------|------------|

| PLUG            | name                           | RE         | C        | PL    | JG       | name                                   | R     | REC        |

| 10 5603 14 XXXX | 861 Parts No.                  | 20 5603 14 | XXXX 861 |       | XXXX 861 | Parts No.                              |       | 4 XXXX 861 |

| LARGE SM        | side view                      | SMALL      | LARGE    |       | SMALL    | side view                              | SMALL |            |

| KEY-A KEY-E     | B type                         | KEY-B      | KEY-A    | KEY-A | KEY-B    | type                                   | KEY-B | KEY-A      |

|                 | 01-01<br>Renesas               |            | ×1       |       |          | 06-06<br>Altera                        |       |            |

|                 | 02-02<br>Renesas               |            |          |       |          | 04-01<br>Renesas                       |       |            |

|                 | 03-03<br>YOKOGAWA              |            |          |       | •        | 04-00<br>Renesas·NEC<br><i>PCI-BUS</i> |       |            |

|                 | 04-04<br>NEC-Toshiba<br>XILINX |            |          |       | •        | 00-00<br>Master                        |       |            |

|                 | 01-05<br>FUJITSU               |            |          |       |          | 01-02<br>Renesas-NEC                   |       |            |

Figure 4.1.1: Keying allocation to prevent incorrect insertion of expansion bus connector.

#### 4.2. Serial interface

A serial interface is used primarily as a debugging console port for connection with a PC. In light of installation space requirements on a T-Engine board, the following compact 15-pin or 16-pin serial connectors are recommended. For this reason, a development kit will usually supply a D-sub-9 (female) cable for connection to a PC.

15-pin serial connector Model: RMC-EA15MY-OM15-MC1 Manufacturer: Honda Tsushin Kogyo

| Pin No. | Signal   |

|---------|----------|

| 1       | GND      |

| 2       | TxD      |

| 3       | RxD      |

| 4       | GND      |

| 5       | RTS      |

| 6       | CTS      |

| 7       | GND      |

| 8       | Reserved |

| 9       | Reserved |

| 10      | Reserved |

| 11      | Reserved |

| 12      | Reserved |

| 13      | Reserved |

| 14      | Reserved |

| 15      | Reserved |

Figure 4.2.1: Overview of recommended connector, and signal requirements

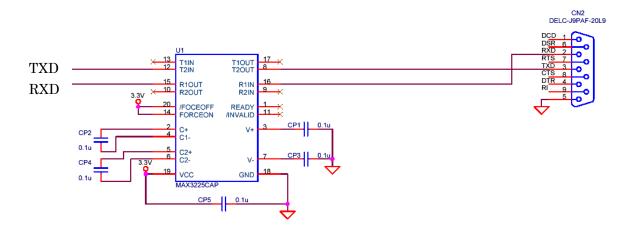

Signal lines comply with the RS-232C standard. An example of drive circuitry is shown in Figure 4.2.2.

To send and receive data in accordance with the counterpart's status, use circuitry in which the RTS/CTS and DTR/DSR signals are linked to each other.

Figure 4.2.2: RS-232C drive circuitry example (from VR5500 T-Engine)

• The baud rate clock circuitry is designed to enable selection of standard speeds from 38.4 to 115.2 Kbps.

## 4.3. PC card interface

The board uses a single Type-II PC card slot with a 68-pin connector, compliant with the PCMCIA Rel.2.1/JEIDA Ver. 4.2 standard. When a card bus — the PC Card Standard for high-speed processing — is needed, the board shall comply with the card bus standard. Three types of spaces — attribute space, memory space, and I/O space — are used. Memory space and I/O space come in two types: 16-bit-access space and 8-bit-access space. Either of these may be chosen in accordance with access method.

Card voltage specifications are 5 V/3.3 V. A power management feature can be used to detect excess power and shut it down, using power supply control circuitry. Card detection and interrupt signals including card interrupts are interfaced to the CPU.

A recommended 68-pin connector is type no. 31-5027-068-130-833+ (from Kyocera Elco).

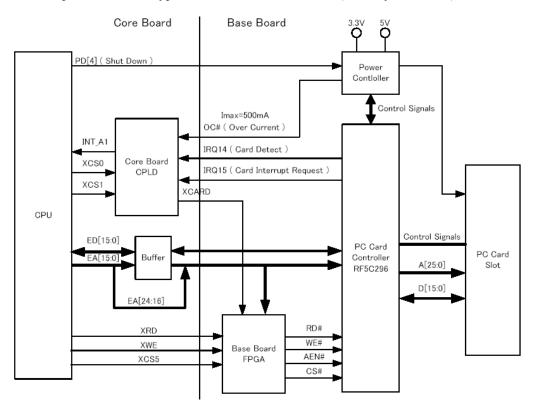

Figure 4.3.1: PC card interface circuitry structure example (from ARM926 T-Engine)

## 4.4. LCD/Touch panel interface

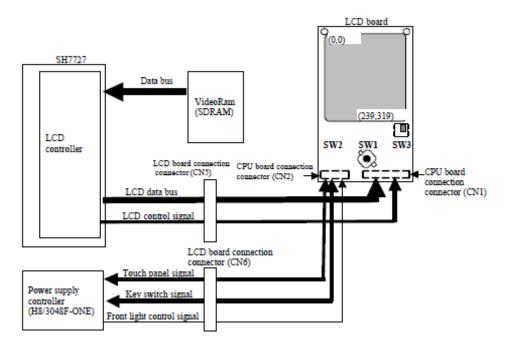

The LCD board shown below, supplied by Renesas, is recommended as the de facto standard T-Engine LCD/touch panel interface. The following figure shows a sample structure.

Figure 4.4.1: Example of connection between LCD board and T-Engine (example using SH7727 T-Engine)

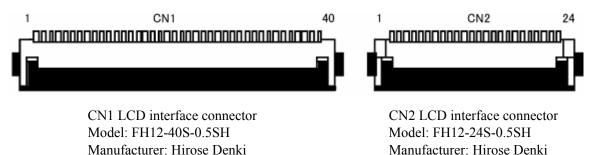

Recommended connector specifications and signal arrangements are shown below.

1) Connector specifications:

## 2) Signal arrangement

## CN1 pin arrangement

| Pin<br>No. | Signal | I/O | Notes        | Pin<br>No. | Signal | I/O | Notes                |

|------------|--------|-----|--------------|------------|--------|-----|----------------------|

| 1          | VBAT   | -   | Power supply | 21         | LCD13  | OUT | LCDC                 |

| 2          | VBAT   | -   | Power supply | 22         | LCD14  | OUT | LCDC                 |

| 3          | VBAT   | -   | Power supply | 23         | LCD15  | OUT | LCDC                 |

| 4          | VBAT   | -   | Power supply | 24         | GND    | -   | Power supply         |

| 5          | NC     | _   | Unused       | 25         | GND    | -   | Power supply         |

| 6          | LCD0   | OUT | LCDC         | 26         | CL1    | OUT | LCDC                 |

| 7          | LCD1   | OUT | LCDC         | 27         | CL2    | OUT | LCDC                 |

| 8          | LCD2   | OUT | LCDC         | 28         | DON    | OUT | LCDC                 |

| 9          | LCD3   | OUT | LCDC         | 29         | M_DISP | OUT | LCDC                 |

| 10         | LCD4   | OUT | LCDC         | 30         | FLM    | OUT | LCDC                 |

| 11         | LCD5   | OUT | LCDC         | 31         | VEPWC  | OUT | LCDC                 |

| 12         | LCD6   | OUT | LCDC         | 32         | VCPWC  | OUT | LCDC                 |

| 13         | LCD7   | OUT | LCDC         | 33         | NC     | —   | Unused               |

| 14         | GND    | -   | Power supply | 34         | GND    | -   | Power supply         |

| 15         | GND    | _   | Power supply | 35         | GND    | -   | Power supply         |

| 16         | LCD8   | OUT | LCDC         | 36         | IR_IN  | IN  | Remote<br>controller |

| 17         | LCD9   | OUT | LCDC         | 37         | 3.3V   | -   | Power supply         |

| 18         | LCD10  | OUT | LCDC         | 38         | 3.3V   | -   | Power supply         |

| 19         | LCD11  | OUT | LCDC         | 39         | 3.3V   | -   | Power supply         |

| 20         | LCD12  | OUT | LCDC         | 40         | 3.3V   | -   | Power supply         |

\* Leave NC and reserved terminals open on the circuit board.

## CN2 pin arrangement

| Pin<br>No. | Signal   | I/O | Notes        | Pin<br>No. | Signal     | I/O | Notes               |

|------------|----------|-----|--------------|------------|------------|-----|---------------------|

| 1          | GND      | —   | Power supply | 13         | ~PAD_CS    | OUT | PAD_I/F             |

| 2          | GND      | —   | Power supply | 14         | ~PAD_IRQ   | IN  | PAD_I/F             |

| 3          | KEY_IN0  | IN  | KEY_I/F      | 15         | PAD_DIN    | OUT | PAD_I/F             |

| 4          | KEY_IN1  | IN  | KEY_I/F      | 16         | PAD_DOUT   | IN  | PAD_I/F             |

| 5          | KEY_IN2  | IN  | KEY_I/F      | 17         | PAD_DCLK   | OUT | PAD_I/F             |

| 6          | KEY_IN3  | IN  | KEY_I/F      | 18         | ~RESET     | OUT | Reset               |

| 7          | KEY_IN4  | IN  | KEY_I/F      | 19         | ~LCD_FLON  | OUT | LCD Power<br>supply |

| 8          | KEY_OUT0 | OUT | KEY_I/F      | 20         | ~LCD_PWRDY | IN  | LCD Power<br>supply |

| 9          | KEY_OUT1 | OUT | KEY_I/F      | 21         | GND        | —   | Power supply        |

| 10         | KEY_OUT2 | OUT | KEY_I/F      | 22         | GND        | _   | Power supply        |

| 11         | GND      | —   | Power supply | 23         | 3.3VSB     | -   | Power supply        |

| 12         | GND      | _   | Power supply | 24         | 3.3VSB     | -   | Power supply        |

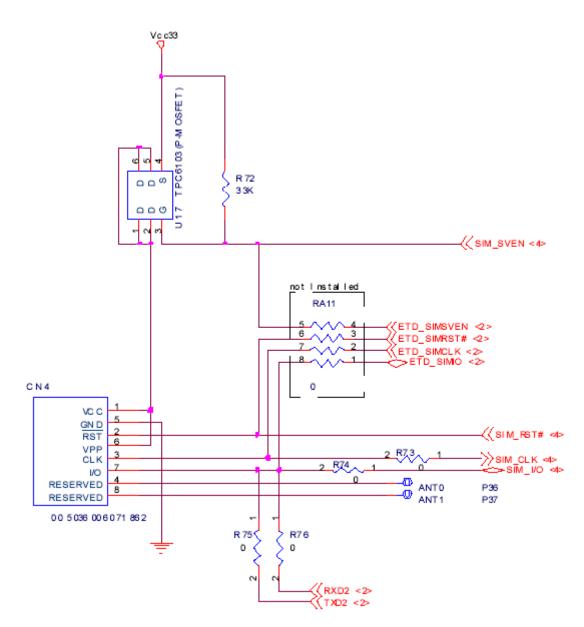

## 4.5. eTRON SIM card interface

Basically, eTRON SIM card interface specifications comply with ISO7816-1 - 3 (SIM). The T=1 protocol is recommended. The T=0 protocol is required at a minimum.

As a connector, the 04-5036-008-110-862 SIM card connector (from Kyocera Elco), which is compatible with the ETSI TS 102221 V4.1.0 VICC-Terminal Interface standard, is recommended.

| PIN No | Signal    | I/O | Function            |

|--------|-----------|-----|---------------------|

| 1      | Vcc 3.3 V | -   | Power supply: 3.3 V |

| 2      | Reset     | 0   | Reset               |

| 3      | Clock     | 0   | Clock*              |

| 4      | Reserved  |     | -                   |

| 5      | GND       | -   | Ground              |

| 6      | Vpp       | -   | NC                  |

| 7      | I/O       | I/O | Serial input/output |

| 8      | Reserved  |     | -                   |

\* Supplied clock

3.5712 MHz Duty: 50±10%

Figure 4.5.1: eTRON SIM connector signals

- The circuitry above is capable of on/off control of the 3.3-V power supply.

- Handle the reserve pins (4, 8) so that they can be connected to on the printed circuit board as terminals.

Figure 4.5.2: Example of eTRON SIM Card interface circuitry (from ARM926 T-Engine)

## • Cautions

(1) Power terminal control:

Since switching between the contact and contactless interface is connected based on whether Vcc power is supplied, a function for shutting of the Vcc power supply is required.

(2) Processing signals from pins 4 and 8:

When using a contactless eTRON SIM card interface, use these pins as terminals for connecting an antenna. Design throughholes near the SIM card connector to enable connection to these terminals.

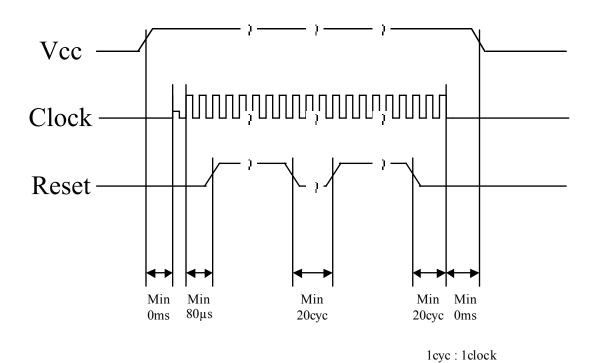

(3) Power sequence:

Figure 4.5.3 shows concerning reset, clock, and power timing.

Figure 4.5.3: Power sequence

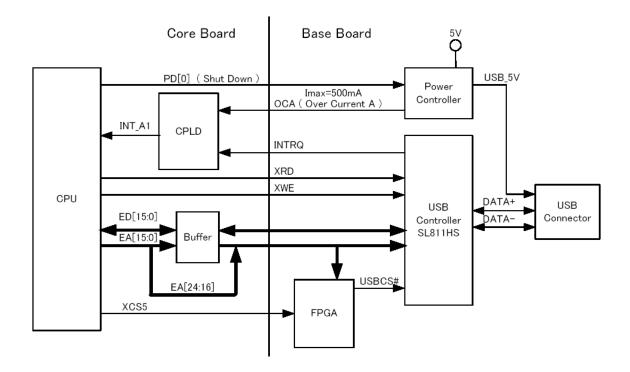

## 4.6. USB host interface

This interface complies with the USB Host Ver. 1.1 (12 M/1.5 Mbps) standard.

If the capacity is available on the T-Engine side's power supply, bus power can be employed to provide a power supply to connected USB devices (max. 5 V/500 mA).

A recommended connector is model no. 20-5041-004-100-834+ (from Kyocera Elco).

|         | Pin No. | Signal | Input/output | Function       |

|---------|---------|--------|--------------|----------------|

|         | 1       | Vcc    | _            | Power supply   |

| 1 2 3 4 | 2       | -Data  | I/O          | - data signals |

|         | 3       | +Data  | I/O          | + data signals |

|         | 4       | GND    | _            | Ground         |

Figure 4.6.1: Connector signal arrangement

Figure 4.6.2: Example of USB interface circuitry (from ARM926 T-Engine)

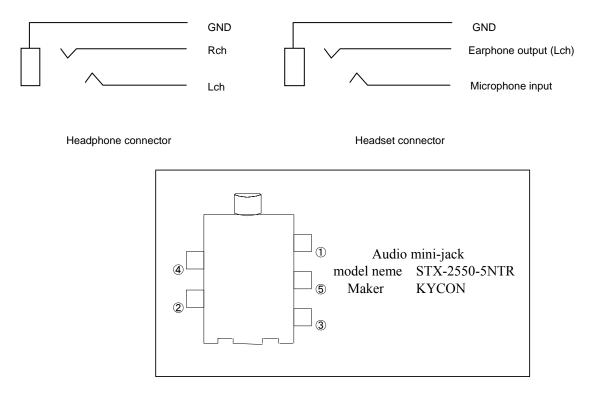

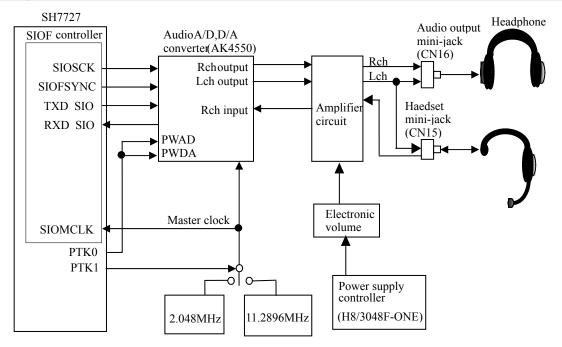

## 4.7. Audio input/output interface

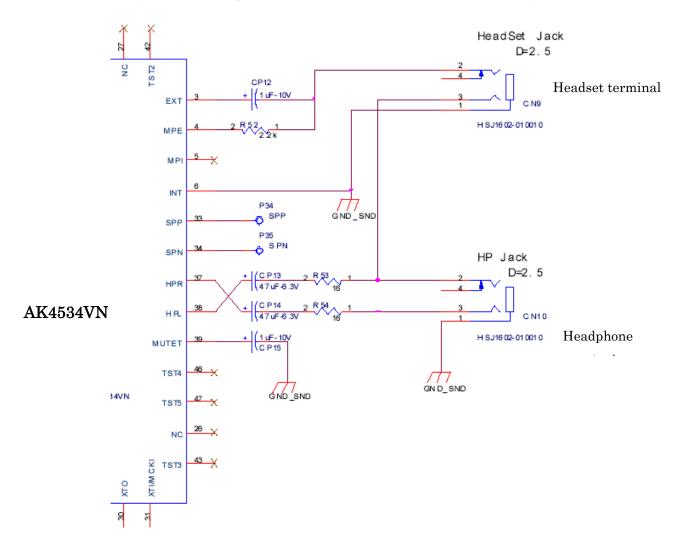

The T-Engine hardware specifications call for signal lines with jacks 2.5 mm in diameter for audio input (monaural) and output (stereo), as shown in the Figure 4.7.1. A recommended connector is model no. HSJ1602-010011 (from Hosiden) and STX-25505NTR (from KYCON). Connect an earphone/microphone output (Lch) to enable use of headsets such as those used with mobile phones.

| Pin No | Signal Name |

|--------|-------------|

| 1      | GND         |

| 2      | R-IN        |

| 3      | R-OUT       |

| 4      | MIC-IN      |

| 5      | HP_SENSE    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • • • • • • • •        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| $H_1 = H_1 $ | innut/output intortooo |

| TI2016 4 / T AU010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | input/output interface |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        |

| Pin No | Signal Name |

|--------|-------------|

| 1      | GND         |

| 2      | L-OUT       |

| 3      | R-OUT       |

| 4      | HP_SENSE    |

| 5      | NC          |

Figure 4.7.2: Audio output interface

Figure 4.7.3: Example of Audio interface structure (from SH7727 T-Engine)

Figure 4.7.4: Example of actual circuitry (from ARM926 T-Engine)

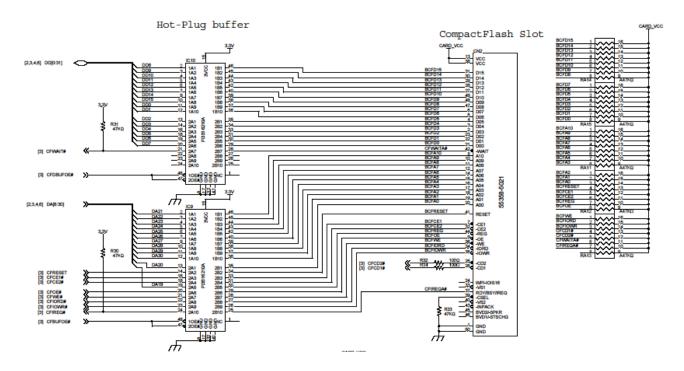

## 4.8. Compact Flash card interface (µT-Engine only)

One Type-II Compact Flash (CF) card slot with a 50-pin connector is used.

A recommended connector is model no. 31-5620-050-716-833+ (from Kyocera Elco).

Interrupt signals are processed to enable hot insertion and removal. Use a power supply voltage of +3.3 V.

Figure 4.8.1: Example of Compact Flash card interface circuitry (from M32104 µT-Engine)

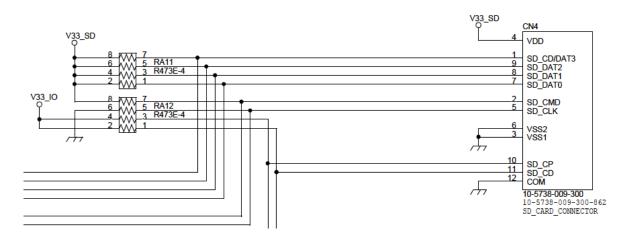

## 4.9. MMC/SD card interface (µT-Engine only)

$\mu$ T-Engine hardware specifications cover MMC- or SD-card connector specifications. Interrupt signals are processed to enable hot insertion and removal. Use a power supply voltage of +3.3 V only.

• Connector specifications:

One nine-pin slot (compatible with cards 2.1 mm thick)

A recommended connector is model no. 10-5738-009-783-862+ (from Kyocera Elco).

Figure 4.9.1: Example of MMC/SD card interface circuitry (from VR4131 µT-Engine)

## 4.10. Power supply interface

4.10.1. Direction of power supply

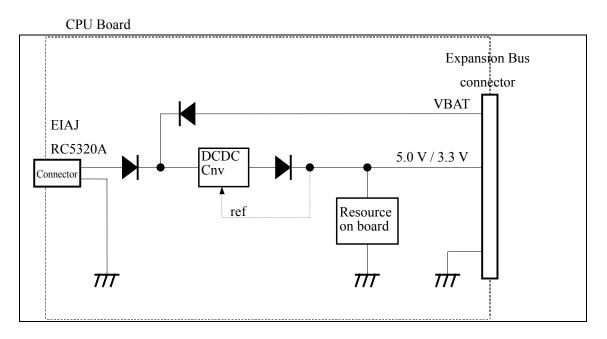

Figure 4.10.1 shows a power supply diagram. The VBAT terminal (133 - 136 pins) on the expansion bus connector supplies power from the expansion board to the CPU board (T-Engine). Other power terminals supply power from the CPU board to the expansion board. For this reason, refer to the Figure 4.10.1 concerning use of diodes to prevent reverse current when inserting devices to the power circuit. For external power supply input, a connector complying with EIAJ RC5320A specifications is implemented. Voltage category 2 (3.15 - 6.3 V) is used, with negative external polarity and positive internal polarity.

Figure 4.10.1: Direction of power supply on the CPU board (T-Engine)

4.10.2 Power state names

Under T-Engine specifications, the following names are used to manage power states. Use of the following names is recommended when designing features such as power management transition-state charts.

| Name: P0<br>State: Main power off                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Name: P1<br>State: Main power on, CPU in sleep mode (can be restarted by interrupt signal), memory not retained,<br>peripheral modules optional |

| Name: P2<br>State: Main power on, CPU in sleep mode (can be restarted by interrupt signal), memory retained,<br>peripheral modules optional     |

| Name: P3<br>State: Main power on, CPU running, memory retained, peripheral modules optional                                                     |

The specifications also include a more detailed naming method for sub-states of state P3, in which the CPU is

running. Under this method, the CPU's lowest operating clock-speed setting is given the suffix "1" and its highest operating clock-speed setting the highest suffix.

Ex.: Low speed: P3-1 Medium speed: P3-2 High speed: P3-3

# 4.10.3. Implementation of power management specifications

T-Engine hardware specifications prescribe the following external power supply control specifications. Implement power management using a power supply controller LSI or similar device.

• External power supply control function

# 1) Controls for turning power on

The following two types of controls for turning the power on are supported:

- Power turned on with power supply

- Power turned on using power switch

It is possible to use a DIP switch or other means to switch between the mode in which the power is turned on with a power supply and the mode in which the power is turned on using a power switch.

Furthermore, it is recommended that controlling turning the power on using power control signals on the expansion bus be supported.

Control of turning the power on using power control signals on the expansion bus should enable expansion boards with functions such as wake on LAN to control the power supply through input of power control signals.

#### 2) Controls for turning power off

- Turning the power off using a power switch

- Turning the power off using other control commands (software control)

- Handling power failures

It is recommended that a T-Engine board have the following functions for handling power

Using a backup power supply (such as UPS or a battery) to detect power failures Any of the following three types of methods may be chosen for implementing detection of power failures using a backup power supply:

- A terminal on the CPU board for input of power failure notification signals

- A function for detecting drops in battery voltage (when using a battery)

- A terminal on the expansion board for input of power failure notification signals, which would then be communicated to the CPU

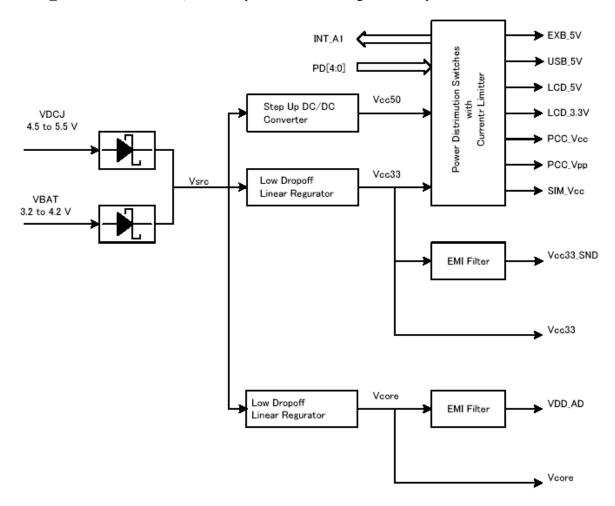

2) Using nonvolatile memory, an RTC internal register, or similar means to detect power failures A function for backing up data (such as on-board nonvolatile memory) is optional. Figure 4.10.2 shows an example of a specific power supply block diagram.

Current restrictions and an on/off switch have been added to the power supply to peripheral devices.

Power on/off control is implemented using PD[0] - PD[4], and INT\_A1 is used to send an interrupt signal when excess power has been detected.

In addition, an optional battery board can be connected, and power can also be supplied from the expansion bus connector's VBAT.

When power is supplied from the DC jack, no power is supplied from the VBAT. Since DC IN must exceed VBAT, care is required when selecting an AC adapter to use.

Figure 4.10.2: Example of power supply block structure (from ARM926 T-Engine)

#### ■ Chapter 5 Power management design for T-Engine hardware

5.1 Power modes (e.g., power save mode)

This section describes implementation methods for each power mode in the T-Engine specifications (i.e., P0, 1, 2, and 3).

Specifications for the P0 mode assume that the main power would be off in this mode. However, since a push type power switch is implemented, power must be connected to the switch to make it operational. For this reason, power is supplied to some circuitry at all times.

Modes P1 and P2 are implemented using software, by setting the MPU to the sleep, doze, stop, or similar states. It is assumed that an MPU with a power management function would be used. In general, power save mode is implemented in one of two ways: by stopping the functioning of the MPU's core only while still running peripheral circuitry or by stopping the MPU's clock and accepting interrupts only. In general, such a state with volatile main memory such as SDRAM not retained is referred to as P1 mode, while such a state with memory retained is referred to as P2 mode.

Mode P3 refers to the state in which the MPU is not set to the sleep, doze, stop, or similar states. Each of modes P1, P2, and P3 assumes changes to the internal state of the MPU only. If no circuitry is added for this purpose, it can be said that there are no differences between these in terms of hardware.

#### 5.2. Power supply controls (power on/off)

Two methods are used for turning the power on: turning the power on with power supply and turning the power on using a power switch. It is possible to use a DIP switch or other means to switch between these methods.

Since T-Engine uses a push type power switch, when controlling the power supply using hardware it is not possible to set power consumption to zero completely. However, the design should enable reducing power consumption to as little as possible.

There are two methods of controlling power supply: implementing hardware logic circuits and via software switches using MPU interrupts. However, when using the latter method the MPU would be set to sleep, doze, stop, or a similar mode when the power is turned off, making it impossible to implement the P0 mode (main power off) covered in the specifications.

The following sections are separated into implementation of hardware and software power control methods.

## 5.2.1. Hardware power-control design

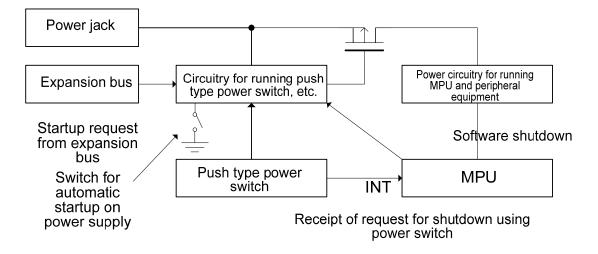

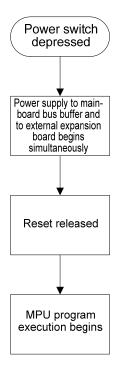

Figure 5.2.1 shows an example structure for implementation of hardware power control.

Figure 5.2.1: Configuration example when power supply control is implemented with hardware.

When the push type power switch is depressed, for startup the power is turned on unconditionally. However, for shutdown the MPU is first notified, and then the MPU cuts off the power.

A switch for automatic startup on power supply is implemented to turn on the power unconditionally when a power supply is attached.

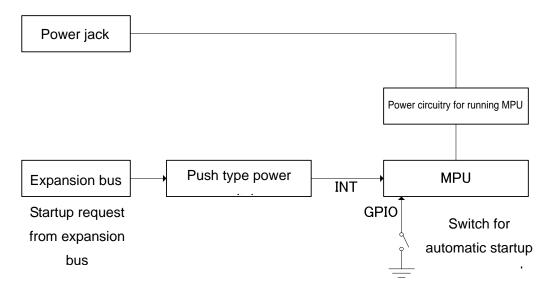

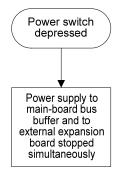

5.2.2. Software power-control design

Figure 5.2.2 shows an example structure for implementation of software power control.

Figure 5.2.2: Configuration example when power supply control is implemented with software.

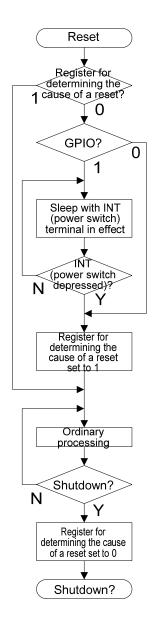

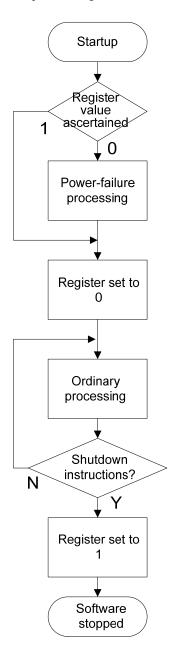

When implementing software power control, a register for determining the cause of a reset, which would not be affected by resetting the MPU, is required. If this register is not included on board the MPU, an external register is used.

Figure 5.2.3 shows the startup software sequence when using a register for determining the cause of a reset. (The initial value of the register for determining the cause of a reset is 0.)

Figure 5.2.3: Startup software sequence

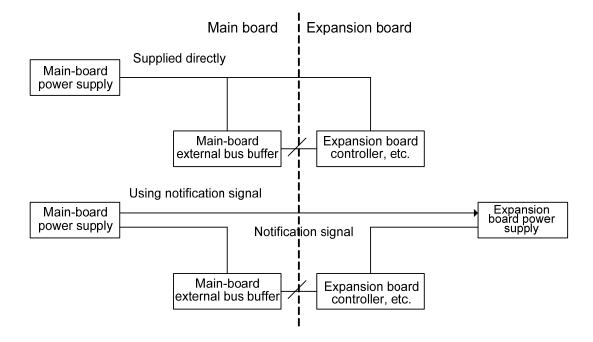

#### 5.3. Linkage with an external expansion board

This section covers points requiring caution when supplying power to an external expansion board through special circuitry for that purpose or when supplying power using the BATT terminal, a specification shared by numerous companies.

Since an external expansion board is connected to the main board using bus wiring, when supplying power or receiving power supply, synchronization with the power supply to the boundary bus buffer and other components must be taken into consideration. Implementation of startup and termination methods in line with the following sample sequence is desirable.

5.3.1 When supplying power to an external expansion board

Figure 5.2.4 shows a sequence diagram for supplying power to an external expansion board on startup.

Figure 5.2.4: Sequence diagram for supplying power